Standar Memori HBM4 Resmi Diluncurkan — Dua Kali Kecepatan dan Efisiensi Daya

Arkadiy Andrienko

Arkadiy Andrienko

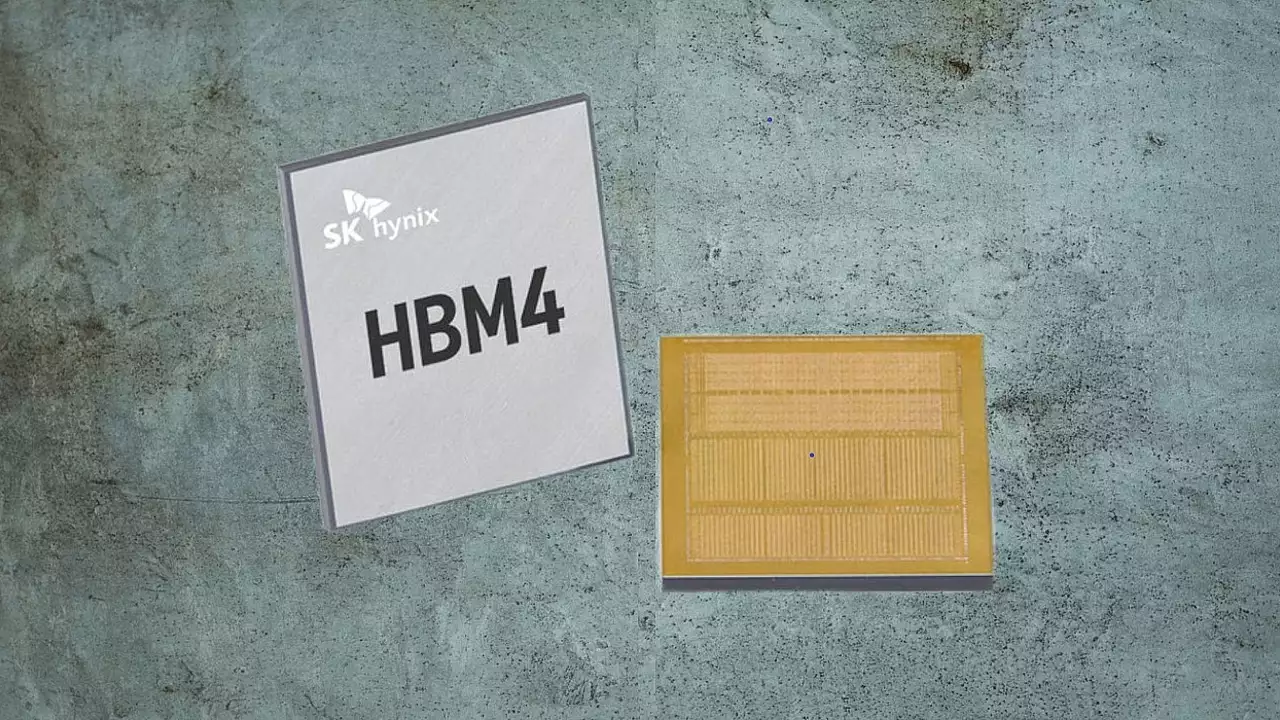

Asosiasi Teknologi Solid State JEDEC telah menyelesaikan spesifikasi HBM4 — generasi berikutnya dari memori bandwidth tinggi. Dirancang untuk memenuhi permintaan yang terus meningkat dari AI, pembelajaran mesin, dan komputasi berkinerja tinggi, standar baru ini menggandakan jumlah saluran independen per tumpukan menjadi 32, memungkinkan paralelisme yang lebih besar dan akses data yang lebih fleksibel. Dengan kecepatan transfer 8 Gbps melalui antarmuka 2048-bit, HBM4 memberikan bandwidth hingga 2 TB/s — peningkatan 60% dibandingkan pendahulunya, HBM3E.

Kefisienan daya ditingkatkan melalui dukungan untuk beberapa domain tegangan (VDDQ dan VDDC), memungkinkan sistem untuk mengoptimalkan konsumsi daya berdasarkan kebutuhan beban kerja. Untuk meningkatkan keandalan, standar ini memperkenalkan Manajemen Penyegaran Terarah (DRFM), yang membantu mengurangi risiko kesalahan memori. HBM4 tetap kompatibel dengan pengontrol HBM3, memudahkan transisi ke generasi baru. Setiap tumpukan memori dapat menampung hingga 64 GB (16 lapisan 32 Gbit), dengan konfigurasi 4-, 8-, dan 12-lapisan juga tersedia.

Para ahli memperkirakan bahwa adopsi luas HBM4 dalam produk komersial akan dimulai pada tahun 2026. Namun, sampel uji awal diharapkan akan mencapai produsen dalam beberapa bulan mendatang, mempercepat pengembangan solusi untuk pusat data, superkomputer, dan akselerator grafis. HBM4 diharapkan menjadi fondasi untuk sistem yang memerlukan kinerja ekstrem — termasuk AI generatif dan simulasi skala besar. Standar yang ditingkatkan ini juga dapat membantu mengurangi konsumsi daya di pusat data dengan mengoptimalkan penanganan volume data yang besar.